- トップページ

- 高度共通 午前1

- 平成27年度秋季問題一覧

- 平成27年度秋季問題7-解答・解説-分析

平成27年度秋季問題

問題7

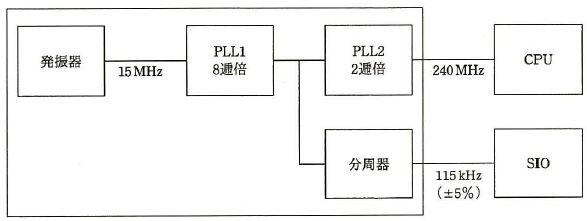

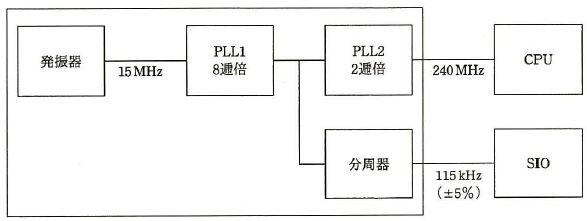

ワンチップマイコンにおける内部クロック発生器のブロック図を示す。 15MHzの発振器と、内部のPLL1、PLL2及び分周器の組合せでCPUに240MHz、シリアル通信(SIO)に115kHzのクロック信号を供給する場合の分周器の値は幾らか。 ここで、シリアル通信のクロック精度は±5%以内に収まればよいものとする。

| ア | 1/24 |

| イ | 1/26 |

| ウ | 1/28 |

| エ | 1/210 |

ワンチップマイコンにおける内部クロック発生器のブロック図を示す。 15MHzの発振器と、内部のPLL1、PLL2及び分周器の組合せでCPUに240MHz、シリアル通信(SIO)に115kHzのクロック信号を供給する場合の分周器の値は幾らか。 ここで、シリアル通信のクロック精度は±5%以内に収まればよいものとする。

| ア | 1/24 |

| イ | 1/26 |

| ウ | 1/28 |

| エ | 1/210 |

解答:エ

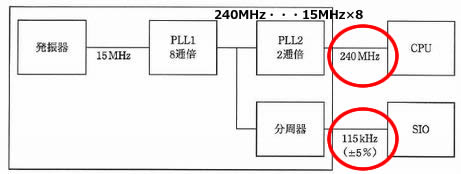

<解説>

入力されたクロックはPLL1で8倍されるのでその出力は120MHz(120,000kHz)である。

これを文周した結果が115kHzである。

| 120,000kHz | × | 1 | =115 |

| n | |||

| n=1043.478 |

したがって、最も近い選択肢はエであり、この時の誤差は2%程度となる。

お問い合わせ