- トップページ

- 応用情報技術者

- 平成23年度秋季問題

- 平成23年度秋季解答・解説

平成23年度秋季解答

問題21

デマンドページング方式による仮想記憶の説明として、適切なものはどれか。

| ア | あるページのアクセス時に、連続する後続のページも主記憶に読み込む。 |

| イ | プログラムで次に必要な手続を指定して、当該ページを主記憶に読み込む。 |

| ウ | プログラムと同時に、処理対象のデータ部分も主記憶に読み込む。 |

| エ | ページフォールトが発生したときに、当該ページを主記憶に読み込む。 |

解答:エ

<解説>

デマンドページング方式とは、メモリ管理方式の一種。デマンド(demand)とは要求,必要を意味する。

プログラム実行中に必要なページが主記憶に存在しない場合(ページフォルト)に必要に応じて必要なページを主記憶装置に割り当てる方式のことである。

デマンドページングに対して、あらかじめ主記憶にページを割当てておく方式のことをプリページングと言う。

| ア | × | プリページング方式の説明である。 |

| イ | × | プリページング方式の説明である。 |

| ウ | × | プリページング方式の説明である。 |

| エ | ○ | デマンドページング方式の説明である。 |

問題22

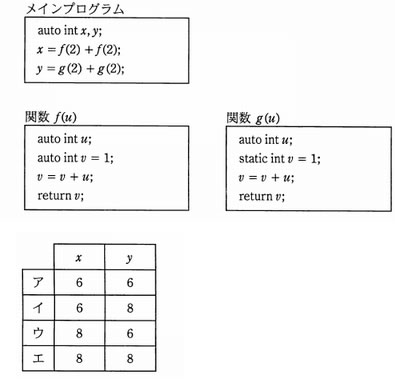

メインプログラムを実行した結果はどれか。ここで、staticは静的割当てを、autoは動的割当てを表す。

解答:イ

<解説>

プログラムの実行時に関数の中で宣言する変数の割当方法には、次のものがある。

- 動的割当

- 動的に割り当てるメモリ領域を使う。

関数終了時に変数はメモリから削除されるため値が残らない。 - 静的割当

- あらかじめ固定されたメモリ領域を使う。

呼び出された関数が終了しても変数自体はメモリ上に存在するので変数の値は残る。

- X=f(2) + f(2)

関数fの変数は動的割当なので関数終了時に変数の値は削除されている。- 1回目のf(2)で2+1=3

- 2回目のf(2)で2+1=3

- 3+3=6

- Y=g(2) +gf(2)

関数gの変数は静的割当なので関数終了時に変数の値は残っている。- 1回目のg(2)で2+1=3

- 2回目のg(2)で3+2=5

- 3+5=8

したがって、イが正解である。

問題23

LSIの故障メカニズムの一つであるESD(Electrostatic Discharge)故障の説明として、適切なものはどれか。

| ア | 機械的な力によって、配線が切断されてしまう現象 |

| イ | 寄生サイリスタの導通によって、半導体素子が破壊されてしまう現象 |

| ウ | 静電気放電によって、半導体素子が破壊されてしまう現象 |

| エ | 電流が過度に流れることによって、配線が切断されてしまう現象 |

解答:ウ

<解説>

ESD(Electrostatic Discharge:静電気放電)とは、人体などに帯同した静電気に静電気放電によって、半導体素子が破壊されてしまう現象のことである。電子機器の誤動作や損傷などの問題を引き起こす原因となる。

| ア | × | 機械的ストレスによる破壊の説明である。 |

| イ | × | ラッチアップの説明である。 |

| ウ | ○ | ESD(Electrostatic Discharge:静電気放電)の説明である。 |

| エ | × | EOS(Electrical OverStress)の説明である。 |

問題24

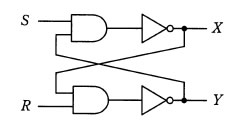

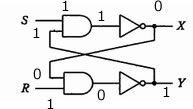

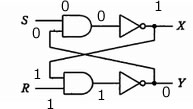

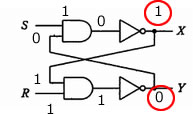

図の論理回路において、S=1、R=1、X=0、Y=1のとき、Sを一旦0にした後、再び1に戻した。この操作を行った後のX、Yの値はどれか。

| ア | X=0,Y=0 |

| イ | X=0,Y=1 |

| ウ | X=1,Y=0 |

| エ | X=1,Y=1 |

解答:ウ

<解説>

- 初期の状態は次のようになる。

- Sをいったん0にすると次のようになる。

- Sを再び1に戻すと次のようになる。

よってウが正解である。

問題25

マイクロプロセッサの省電力対策に関する記述のうち、適切なものはどれか。

| ア | CMOSよりもバイポーラ素子を使用した方が、消費電力を少なくできる。 |

| イ | CMOSを使用したプロセッサでは、動作周波数を低くすることによって、論理反転時の電流が減少し、消費電力を少なくできる。 |

| ウ | クロックゲーティング方式を使用すると、スタンバイ時にプロセッサに対する電圧供給を停止できるので、消費電力を少なくできる。 |

| エ | 動作電圧を高くすることによって、内部の演算処理が高速になり、消費電力を少なくできる。 |

解答:イ

<解説>

| ア | × | ハイポーラは電力の強さによって増幅を行なうトランジスタであり、常に電流を流す必要があるので消費電力が大きい。CMOSは電界効果トランジスタが用いられ電圧によって増進するので消費電力は小さい。 すなわち、バイポーラ素子よりもCMOSを使用した方が、消費電力を少なくできる。 |

| イ | ○ | CMOSを使用したプロセッサでは、動作周波数を低くすることによって、論理反転時の電流が減少し、消費電力を少なくできる。 |

| ウ | × | クロックゲーティング方式は、動作していない論理回路のクロックの供給を停止する技術である。 クロックゲーティング方式は、スタンバイ時の省電力化ではない。 |

| エ | × | 動作電圧を高くすることによって、内部の演算処理が高速になる半面、消費電力は多くなる。 |

お問い合わせ