- トップページ

- 基本情報技術者

- 平成18年度春季問題

- 平成18年度春季解答・解説

平成18年度春季解答

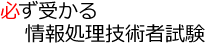

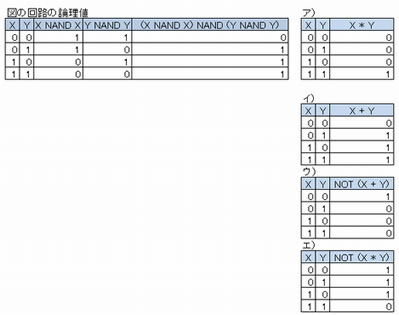

問題16

NAND 回路による次の組合せ回路の出力 Z を表す式はどれか。ここで, は NAND 回路,・ は論理積,+は論理和,Xは X の否定を表す。

は NAND 回路,・ は論理積,+は論理和,Xは X の否定を表す。

| ア | X・Y |

| イ | X+Y |

| ウ | X+Y |

| エ | X・Y |

解答:イ

<解説>

下図よりイが正解である。

問題17

プロセッサにおけるパイプライン処理方式を説明したものはどれか。

| ア | 単一の命令を基に、複数のデータに対して複数のプロセッサが同期をとりながら並列的にそれぞれのデータを処理する方式 |

| イ | 一つのプロセッサにおいて、単一の命令に対する実行時間をできるだけ短くする方式 |

| ウ | 一つのプロセッサにおいて、複数の命令を少しずつ段階をずらしながら同時実行する方式 |

| エ | 複数のプロセッサが、それぞれ独自の命令を基に複数のデータを処理する方式 |

解答:ウ

<解説>

| ア | × | SIMD(Single Instruction Multiple Data Stream)方式に関する説明である。 |

| イ | × | SISD(Single Instruction Single Data Stream)方式に関する説明である。 |

| ウ | ○ | パイプライン処理方式に関する説明である。 |

| エ | × | MIMD(Multiple Instruction Multiple Data Stream)方式に関する説明である |

問題18

コンピュータの命令実行順序として、適切なものはどれか。

| ア | オペランド読出し → 命令の解読 → 命令フェッチ → 命令の実行 |

| イ | オペランド読出し → 命令フェッチ → 命令の解読 → 命令の実行 |

| ウ | 命令の解読 → 命令フェッチ → オペランド読出し → 命令の実行 |

| エ | 命令フェッチ → 命令の解読 → オペランド読出し → 命令の実行 |

解答:エ

<解説>

プロセッサがプログラムを処理する順序は

- プログラムの命令をプログラムが格納されているメモリから読み出す(命令フェッチ)

- 読み出した命令をCPU内で処理できる形に変形する(命令の解読(デコード))

- 必要なデータを取り出してレジスタに格納する(オペランド読出し)

- 実際に命令を処理する(命令実行)

の順に行われる。

よってエが正解である。

問題19

あるベンチマークテストプログラムの命令ごとの出現頻度と、これを実行するプロセッサの実行クロック数を表に示す。このベンチマークテストプログラムにおけるCPI ( Clocks Per Instruction )は幾らか。

| ア | 0.48 |

| イ | 0.69 |

| ウ | 2.10 |

| エ | 2.67 |

解答:ウ

<解説>

CPIは1命令の実行に必要なクロック数を表す。

| CPI | = | 0.5×1+0.3×2+0.2×5 |

| = | 2.10 |

よってウが正解である。

問題20

50 MIPS のプロセッサの平均命令実行時間は幾らか。

| ア | 20 ナノ秒 |

| イ | 50 ナノ秒 |

| ウ | 2 マイクロ秒 |

| エ | 5 マイクロ秒 |

解答:ア

<解説>

1MIPSでは、1秒間に1× 10 6 の命令を実行することができる。

したがって、50 MIPS では、1秒間に50× 10 6 の命令を実行することができる。

1命令にかかる時間 = 1÷(50×106) = 0.00000002(秒) = 20 × 10 -9秒 = 20ナノ秒

よってアが正解である。

お問い合わせ